Khi các yêu cầu của AI (Artificial Intelligence - trí tuệ nhân tạo) và HPC (High Performance Computing - điện toán hiệu năng cao) ngày càng tăng về hiệu năng, dung lượng và hiệu quả năng lượng, FMC (Ferroelectric Memory Company) đã nghiên cứu, phát triển công nghệ DRAM+. FMC DRAM+ sẽ hợp tác thương mại hóa cùng với Neumonda, hứa hẹn là giải pháp đáp ứng được trong thời đại bùng nổ AI, nhờ tốc độ truy xuất nhanh như DRAM (Dynamic Random Access Memory) và khả năng lưu trữ dữ liệu bền bỉ như SSD. 2 đặc tính này từ trước tới nay vốn không chung 1 thuyền khi DRAM có tốc độ truy xuất cực nhanh nhưng dữ liệu lưu trữ là khả biến (volatile), hoàn toàn “bốc hơi” khi mất điện, còn SSD thì ngược lại, truy xuất chậm hơn, bù lại dữ liệu bất biến (non-volatile).

Nếu như các loại DRAM quen thuộc như DDR3, DDR4 hay DDR5 đều có tiêu chuẩn chính thức được JEDEC (Joint Electron Device Engineering Council) công bố thì DRAM+ hoàn toàn ngược lại. Tính tới thời điểm hiện tại, DRAM+ không phải là 1 tiêu chuẩn bộ nhớ mà nó mới chỉ là tên thương mại do DMC và đối tác Neumonda sử dụng. DRAM+ dùng để chỉ 1 kiến trúc bộ nhớ sắt điện (FeRAM - Ferroelectric Random Access Memory) cụ thể do FMC phát triển.

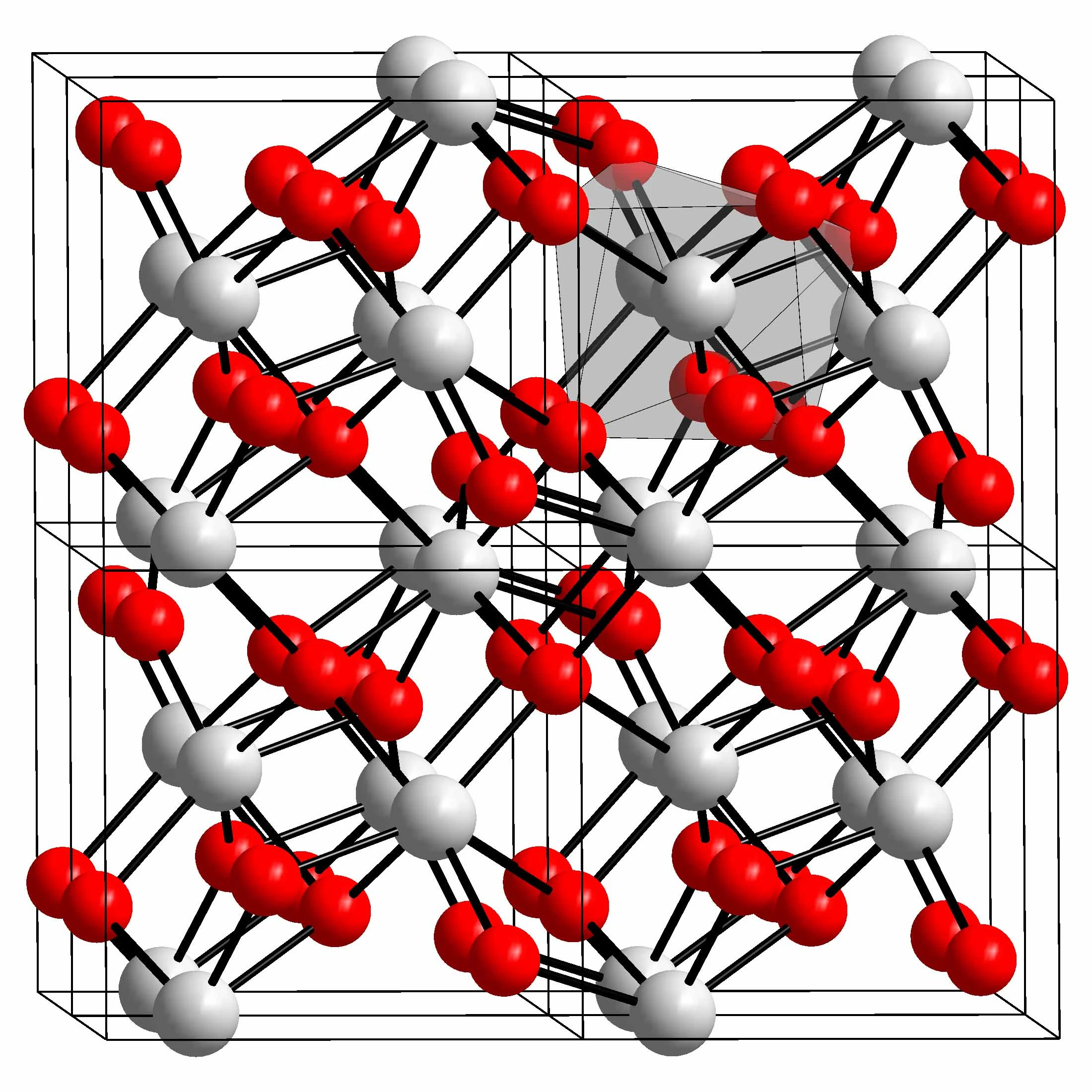

Công nghệ cốt lõi đứng đằng sau DRAM+ là việc sử dụng vật liệu Hafnium Oxide (HfO₂) có đặc tính sắt điện (ferroelectric) để thay thế cho các tụ điện (capacitor) truyền thống trong cấu trúc ô nhớ DRAM (DRAM có cấu trúc gồm nhiều ô nhớ, mỗi ô nhớ chứa 1 tụ điện và 1 transistor). Sự thay đổi này cho phép ô nhớ lưu trữ dữ liệu một cách bền bỉ mà không cần nguồn điện duy trì, đồng thời vẫn giữ được tốc độ truy xuất nhanh đặc trưng của DRAM. Do đó, DRAM+ thực chất là một dạng FeRAM cải tiến dựa trên HfO₂, được phát triển như một giải pháp bộ nhớ lai (hybrid memory) giữa DRAM và lưu trữ flash.

DRAM+ như đã nói, đang là tên thương mại thay vì tiêu chuẩn công nghiệp, yếu tố này rất quan trọng. Lý do là công nghệ DRAM+ hiện đang gắn liền với FMC và Neumonda, từ đó dẫn tới việc áp dụng rộng rãi sẽ phụ thuộc vào chiến lược thương mại hóa và cấp phép của các công ty này. Nếu DRAM+ là 1 tiêu chuẩn công nghiệp thì thị trường sẽ dễ dàng có nhiều bên cùng tham gia cung cấp sản phẩm hơn.

Tốc độ truyền dữ liệu và tốc độ truy xuất của DRAM+ được cho là tương đương với DRAM truyền thống, đơn vị ns (nanosecond). Điều này cho thấy mục tiêu hiệu năng của DRAM+ là ngang ngửa với các DRAM tiêu chuẩn công nghiệp hiện tại. Trong khi đó mật độ của DRAM+ nguyên mẫu (prototype) là ở phạm vi Gigabit. Công nghệ HfO₂ có khả năng mở rộng xuống dưới tiến trình 10 nm, cho phép đạt mật độ cao hơn, tiềm năng lên đến phạm vi Gigabyte, gần với DRAM truyền thống. Dung lượng cụ thể của DRAM+ thương mại chưa có thông tin rõ ràng, tuy nhiên có thể ở mức Gigabyte trên mỗi thanh.

Mục tiêu của DRAM+ là giảm đáng kể điện năng tiêu thụ tĩnh (static power consumption) so với DRAM truyền thống. DRAM thông thường sẽ có các chu kỳ làm mới bit dữ liệu (refresh cycle) để duy trì bit đó, do khi mất điện sẽ mất dữ liệu. Dữ liệu lưu trữ trên DRAM+ là bất biến nên không cần refresh cycle, từ đó giảm điện năng tiêu thụ tĩnh. Đặc điểm này rất quan trọng ở những ứng dụng cần tiết kiệm năng lượng và khả năng mở rộng lớn.

Mục tiêu độ trễ của DRAM+ là ở mức ns, tức là nó nhắm tới ngang bằng với các chuẩn bộ nhớ hiện tại (DDRx), vượt trội hơn độ trễ của các chip nhớ NAND flash. Nếu độ trễ quá cao, DRAM+ sẽ mất đi ý nghĩa phát triển và không có cải tiến nào so với FeRAM trước đây. Bên cạnh đó, DRAM+ sẽ có tính bền về dữ liệu, lưu trữ bất biến kể cả khi không được cấp nguồn điện. Chưa có thông tin về độ bền ghi xóa (write endurance) và khả năng duy trì dữ liệu (data retention) của DRAM+.

Vậy còn giao diện (interface) của DRAM+ thì sao? Hiện tại chưa có thông tin cụ thể về giao diện DRAM+, nhưng nó tương thích với quy trình chế tạo, sản xuất DRAM truyền thống dưới 10 nm của các hãng lớn như Micron, Samsung và SK hynix. Điều này dẫn tới suy đoán rằng DRAM+ sẽ có thể dùng các công nghệ giao diện tương tự, hoặc là sẽ tương thích với các chuẩn DRAM hiện tại. Dĩ nhiên nếu DRAM+ sử dụng kiểu giao diện khe cắm đã chuẩn hóa tương tự như DDRx thì sẽ giảm chi phí đầu tư (phát triển và thay thế giao diện mới).

Về cơ bản, DRAM+ có cải tiến nền tảng là thay thế thành phần lưu trữ điện tích truyền thống trong ô nhớ DRAM. Thay vì sử dụng tụ điện (capacitor) thông thường vốn bị rò rỉ điện tích và yêu cầu làm mới định kỳ (refresh), DRAM+ sử dụng một phần tử dựa trên vật liệu Hafnium Oxide (HfO₂) có đặc tính sắt điện (ferroelectric).

Vật liệu sắt điện như HfO₂ có khả năng duy trì 1 trong 2 trạng thái phân cực điện (electric polarization) ổn định ngay cả khi không có điện áp đặt vào. Hai trạng thái phân cực này có thể được sử dụng để biểu diễn logic '0' và '1'. Khi một điện áp được đặt vào, trạng thái phân cực có thể được chuyển đổi, tương ứng với thao tác ghi dữ liệu, trong khi đó quá trình đọc dữ liệu sẽ dựa trên việc phát hiện trạng thái phân cực hiện tại. Do trạng thái phân cực được duy trì mà không cần nguồn điện, bộ nhớ trở nên bất biến (non-volatile). Cấu trúc ô nhớ cơ bản vẫn có thể là dạng 1T1C (1 Transistor - 1 Tụ điện/Phần tử sắt điện), trong đó transistor đóng vai trò cổng truy cập để đọc/ghi vào phần tử sắt điện.

DRAM truyền thống lưu trữ dữ liệu dưới dạng điện tích trên tụ điện. Điện tích này bị rò rỉ nhanh chóng, đòi hỏi chu kỳ làm mới liên tục (vài ms một lần), gây tiêu tốn năng lượng tĩnh và 1 số trường hợp còn làm tăng độ trễ. Nhờ HfO₂ nênDRAM+ loại bỏ nhu cầu làm mới, tiết kiệm năng lượng hơn DRAM. Bù lại DRAM có tốc độ ghi nhanh hơn và độ bền coi như không có (tới hơn 1 triệu tỷ chu kỳ ghi xóa, trong khi SLC NAND flash khoảng 100,000 chu kỳ). Độ bền của DRAM+ chưa có thông tin cụ thể nhưng thường sẽ thấp hơn DRAM.

Còn các thế hệ FeRAM trước đây thường sử dụng PTZ (Lead Zirconate Titanate) và gặp nhiều hạn chế. PTZ rất khó để thu nhỏ kích thước bằng tiến trình công nghệ, do đó cải tiến sẽ khó khăn. Để sản xuất PTZ bằng quy trình CMOS (Complementary Metal-Oxide-Semiconductor) tiêu chuẩn cực kỳ phức tạp và tốn kém chi phí, trong khi đây là quy trình chế tạo IC có giá thành rẻ. Do đó, FeRAM sử dụng PTZ có kích thước ô nhớ lớn và mật độ lưu trữ thấp, khó đáp ứng được cho các ứng dụng hiện đại. Ngược lại, DRAM+ xài HfO₂ là loại vật liệu đã được sử dụng trong ngành công nghiệp bán dẫn, tương thích tốt với các quy trình CMOS hiện có. Điều này giúp đơn giản hóa và giảm chi phí tích hợp sản xuất.

HfO₂ cho thấy khả năng mở rộng tốt xuống các quy trình công nghệ tiên tiến, dưới 10 nm. Đây là điểm quan trọng mở ra tiềm năng đạt được mật độ lưu trữ cao hơn nhiều so với PZT FeRAM, tiến gần đến mật độ của DRAM (tức là mức Gigabyte thay vì Megabyte) - yếu tố then chốt giúp công nghệ DRAM+ có thể cạnh tranh về mặt chi phí và dung lượng trong các ứng dụng đòi hỏi bộ nhớ lớn (AI, HPC).

DRAM+ cũng sẽ thu hẹp khoảng cách giữa DRAM và NAND Flash hiện tại. HfO₂ FeRAM được định vị như cầu nối giữa bộ nhớ chính DRAM và lưu trữ NAND Flash. Nó có độ trễ truy xuất thấp và tốc độ cao của DRAM, kết hợp với tính bền bỉ của NAND Flash. Các công nghệ Bộ nhớ Lớp Lưu trữ (Storage Class Memory - SCM) trước đây như Intel Optane cũng nhắm đến mục tiêu này nhưng gặp nhiều thách thức về chi phí và hệ sinh thái. Việc kết hợp các đặc tính tốt nhất của cả 2 loại bộ nhớ cho phép phát triển các kiến trúc hệ thống mới, có khả năng đơn giản hóa hệ thống phân cấp bộ nhớ và cải thiện hiệu năng tổng thể, đặc biệt đối với các ứng dụng truy cập dữ liệu thường xuyên.

DRAM+ không nhắm đến việc thay thế hoàn toàn DRAM hoặc NAND Flash trong mọi ứng dụng, mà tập trung vào các thị trường và lĩnh vực cụ thể nơi các đặc tính độc đáo của nó mang lại giá trị cao nhất. Đầu tiên, các hệ thống AI, đặc biệt là trong giai đoạn huấn luyện (training) và suy luận (inference), thường yêu cầu truy cập nhanh vào các trọng số mô hình (model weights) lớn. Việc lưu trữ các trọng số này trong bộ nhớ bất biến như DRAM+ cho phép khởi động nhanh hơn, giảm nhu cầu nạp lại dữ liệu từ bộ nhớ lưu trữ chậm hơn, đồng thời tiết kiệm năng lượng so với việc giữ chúng trong DRAM truyền thống. Khả năng duy trì dữ liệu khi mất điện cũng tăng cường độ tin cậy cho các tác vụ AI kéo dài.

DRAM+ cũng có ứng dụng đối với xe hơi, nơi các bộ điều khiển điện tử (ECU) trong xe hiện đại ngày càng phức tạp, xử lý lượng lớn dữ liệu và yêu cầu khả năng khởi động gần như tức thời. Tính bất biến của DRAM+ cho phép lưu trữ trạng thái hệ thống và dữ liệu cấu hình quan trọng, giúp xe khởi động nhanh hơn sau khi tắt máy hoặc trong trường hợp mất điện tạm thời. Khả năng hoạt động tin cậy trong dải nhiệt độ rộng và tiết kiệm năng lượng cũng là những yếu tố quan trọng trong môi trường xe hơi.

Lĩnh vực y tế có các thiết bị cấy ghép bên trong cơ thể người (medical implant), thường có yêu cầu cực kỳ khắt khe về điện năng tiêu thụ do giới hạn về pin và kích thước. Việc DRAM+ loại bỏ chu kỳ làm mới và có mức tiêu thụ điện tĩnh thấp khiến nó trở thành lựa chọn hấp dẫn cho việc lưu trữ dữ liệu hoặc mã chương trình trong các thiết bị này, kéo dài tuổi thọ pin và đảm bảo hoạt động ổn định.

Các hệ thống điều khiển công nghiệp, IoT công nghiệp (IIoT) và các thiết bị nhúng khác thường hoạt động trong môi trường khắc nghiệt, yêu cầu độ tin cậy cao cùng khả năng lưu trữ dữ liệu bền bỉ. DRAM+ có thể cung cấp giải pháp bộ nhớ tốc độ cao, tiết kiệm năng lượng và có khả năng chống chịu tốt hơn với các biến động năng lượng (nguồn cấp điện).

DRAM+ còn có nhiều tiềm năng khi nói về hệ thống nhúng thực thi tại chỗ (XIP - eXecute-In-Place). Tính bất biến và tốc độ truy xuất nhanh của công nghệ này, về mặt lý thuyết, cho phép vi xử lý thực thi mã chương trình trực tiếp từ DRAM+ mà không cần tải vào RAM riêng, từ đó giảm thời gian khởi động, đơn giản hóa thiết kế hệ thống và tiết kiệm năng lượng.

Từ trái sang: Marco Mezger, COO của Neumonda, Thomas Rueckes, CEO của FMC, và Peter Poechmueller, CEO của Neumonda mừng sự hợp tác giữa 2 công ty.

Hợp tác chiến lược giữa FMC sở hữu công nghệ DRAM+ dựa trên HfO₂ FeRAM và Neumonda - công ty có chuyên chuyên môn sâu về bộ nhớ và sở hữu các nền tảng kiểm thử bộ nhớ tiên tiến, chi phí thấp (Rhinoe, Octopus, Raptor) để phát triển và thương mại hóa DRAM+. Cả FMC và Neumonda đều có trụ sở tại Đức, cùng tầm nhìn khôi phục ngành thiết kế và sản xuất bộ nhớ bán dẫn tại Đức và châu Âu. FMC phát triển DRAM+ còn Neumonda hỗ trợ trong thiết kế, kiểm thử, tư vấn và tiếp thị sản phẩm. Hiện tại DRAM+ đã vượt qua giai đoạn nghiên cứu cơ bản. FMC đã phát triển thành công công nghệ và tạo ra các nguyên mẫu (prototype) chứng minh khả năng đạt mật độ lưu trữ ở phạm vi Gigabit. Dự án này đang trong giai đoạn kiểm thử (testing) và tiền thương mại hóa (pre-commercialization), tận dụng các nền tảng kiểm thử của Neumonda để đẩy nhanh quá trình phát triển và đảm bảo chất lượng sản phẩm.

Tham vọng của FMC lớn hơn nhiều và không chỉ dừng lại ở DRAM+. Công ty cũng đang phát triển một dòng sản phẩm khác dựa trên HfO₂ FeRAM, có tên là Cache+. Đây là bộ nhớ cache bất biến dưới dạng chiplet. Mục tiêu của Cache+ là tích hợp khả năng lưu trữ bền bỉ và mật độ cao hơn vào bộ nhớ đệm (cache), đặc biệt nhắm đến việc tăng tốc các ứng dụng suy luận AI. Điều này cho thấy chiến lược nền tảng rộng hơn của FMC, công nghệ HfO₂ FeRAM có thể được điều chỉnh để phục vụ các cấp độ khác nhau trong hệ thống phân cấp bộ nhớ, từ bộ nhớ chính (DRAM+) đến bộ nhớ cache (Cache+) nằm gần bộ xử lý hơn.

Những thách thức mà DRAM+ phải đối mặt, đầu tiên là sản xuất quy mô lớn. Khi cần chuyển đổi từ sản xuất nguyên mẫu sang sản xuất hàng loạt với chi phí hiệu quả là một rào cản cần vượt qua. Việc tìm kiếm đối tác gia công (foundry) phù hợp hoặc tự chủ được năng lực sản xuất tại châu Âu đòi hỏi vốn đầu tư lớn và thời gian dài. Kế đó là khả năng cạnh tranh khi DRAM và NAND Flash là những công nghệ đã trưởng thành, cực kỳ tối ưu về chi phí nhờ sản xuất ở quy mô khổng lồ. DRAM+ sẽ phải cạnh tranh về giá trên mỗi bit (cost-per-bit) với các công nghệ này, đặc biệt là trong các thị trường nhạy cảm về giá. Bên cạnh đó, chi phí kiểm thử cũng là một yếu tố quan trọng cần tối ưu để không quá ảnh hưởng vào giá thành cuối.

Mặc dù HfO₂ FeRAM khá hứa hẹn, nhưng cần có dữ liệu thực nghiệm về độ bền ghi xóa (write endurance) và khả năng duy trì dữ liệu (data retention) trong dài hạn để có thêm cơ sở về độ tin cậy, đặc biệt đối với các ứng dụng quan trọng như xe hơi và y tế. Các công nghệ NVM (Non-Volatile Memory) thường phải đánh đổi giữa các yếu tố này.

Việc phát triển hệ sinh thái cũng là yếu tố then chốt cần quan tâm. Sự thành công của một công nghệ bộ nhớ mới không chỉ nằm ở bản thân con chip mà còn phụ thuộc vào hỗ trợ từ toàn bộ hệ sinh thái xoay quanh. Những thứ này bao gồm điều khiển bộ nhớ (memory controller), các nhà thiết kế hệ thống, hệ điều hành và phát triển ứng dụng. Lịch sử của các công nghệ bộ nhớ bất biến mới nổi như Intel Optane (dựa trên 3D XPoint), cho thấy con đường này không hề dễ dàng. Dù có những ưu điểm kỹ thuật nhưng Optane đã phải vật lộn để có được sự chấp nhận rộng rãi, phần lớn do các yếu tố như chi phí cao hơn DRAM, sự phức tạp trong việc tích hợp vào hệ sinh thái phần mềm và phần cứng hiện có. Đặc biệt khi khó xác định các ứng dụng "sát thủ" nơi ích lợi của nó thực sự vượt trội so với các giải pháp thay thế khác (nôm na là ứng dụng mà sản phẩm mới đó thực sự nổi bật và đánh bại các đối thủ khác). DRAM+ cũng sẽ phải đối mặt với những thách thức tương tự trên lộ trình tương lai. Thành công không chỉ phụ thuộc vào việc đạt được các thông số kỹ thuật ấn tượng mà còn cần chứng minh được độ tin cậy dài hạn, xây dựng một hệ sinh thái hỗ trợ mạnh mẽ và đưa ra một mức giá cạnh tranh đủ để thuyết phục khách hàng, để rồi họ dần chuyển đổi khỏi các công nghệ đã được kiểm chứng như DRAM và NAND Flash.Nguồn:tinhte.vn/thread/tim-hieu-cong-nghe-dram-danh-cho-linh-vuc-ai-va-hpc.4012564/